4 Articles

Tags :semiconductor-eda

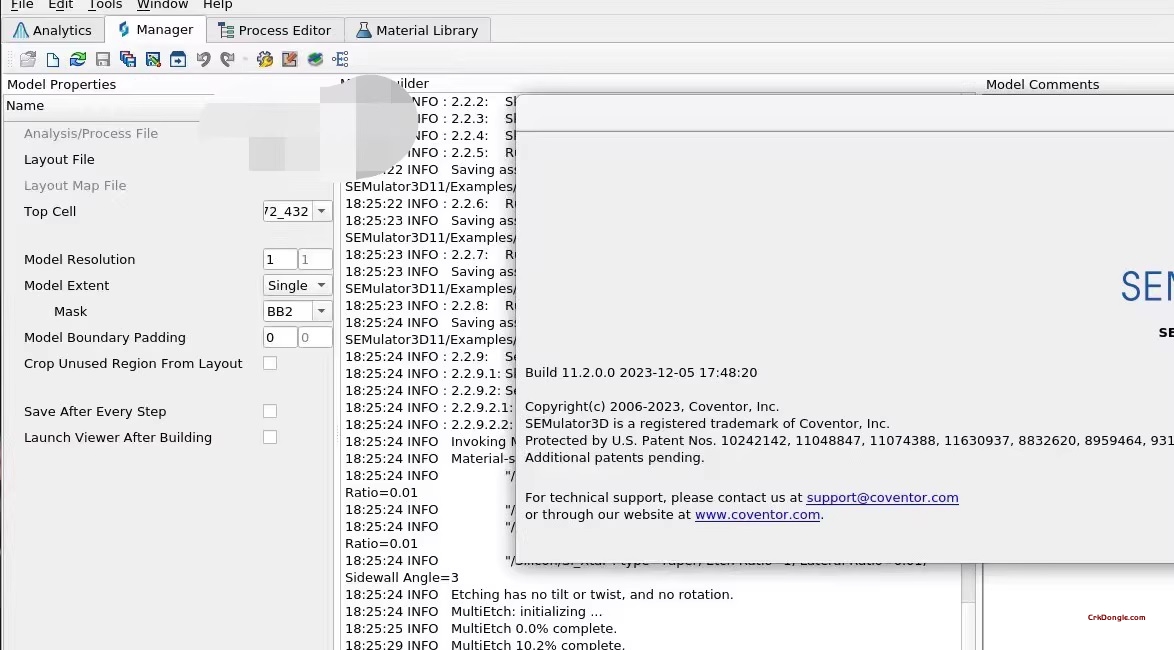

Coventor SEMulator3D 11.2: The Definitive Platform for 3D Semiconductor Virtual Fabrication Coventor SEMulator3D 11.2 is the industry-leading software solution for virtual fabrication and predictive process modeling of the world’s most advanced 3D semiconductor devices and advanced packaging architectures. As part of the Ansys portfolio, it enables process engineers, integration engineers, and device designers to build and analyze a complete digital twin of the complex 3D manufacturing process flow. By emulating hundreds of sequential process steps (deposition, etch, CMP, lithography), SEMulator3D predicts the exact 3D geometry, electrical parasitics, and structural variations that will result on the silicon wafer, long before committing to costly and time-consuming fab experiments. Core Philosophy: “Fab-in-a-Box” for Predictive Process Development SEMulator3D’s power lies in its rule-based, voxel...

Cadence Stratus 2025: The High-Level Synthesis Powerhouse for RTL Generation Cadence Stratus 2025 is a premier high-level synthesis (HLS) platform that fundamentally transforms the digital design workflow. It empowers hardware architects and design engineers to describe complex functionality and algorithms at a high abstraction level—using C++, SystemC, or MATLAB—and then automatically synthesize this behavioral description into optimized, high-quality, and cycle-accurate RTL (Verilog/VHDL). By elevating the starting point of design, Stratus dramatically increases productivity, enables architectural exploration, and accelerates the development of sophisticated IP for applications in AI/ML acceleration, advanced DSP, image processing, and communication systems. Core Technology & Key Capabilities: 1. High-Abstraction Design Entry & Synthesis C++ & SystemC Synthesis: Accepts industry-standard ANSI C++ and SystemC as input, allowing algorithms...

Questa OneSpin Static Formal 2025: The Exhaustive Verification Platform for Zero-Defect Designs Questa OneSpin Static Formal 2025 represents the industry’s most advanced static formal verification platform, designed for engineers who require mathematical certainty in their ASIC, FPGA, and IP designs. Unlike traditional simulation, which tests only a subset of possible scenarios, static formal verification uses rigorous mathematical proof techniques to exhaustively analyze a design against its specifications. This makes it an indispensable tool for verifying safety-critical hardware in automotive (ISO 26262), aerospace, and medical applications where a single undetected bug can have catastrophic consequences. Core Technology & Key Capabilities: 1. Formal Property Verification (FPV) This is the flagship application, enabling engineers to prove that a design’s behavior matches its intended...

Cadence Integrity 3D-IC 2025: The Unified Platform for Next-Generation Heterogeneous Integration Cadence Integrity 3D-IC 2025 is the industry-leading electronic design automation (EDA) platform specifically architected for the complexities of designing modern three-dimensional integrated circuits (3D-ICs) and multi-chiplet systems. It provides a cohesive, start-to-finish environment that unifies system-level planning, physical implementation, and signoff analysis—a critical requirement for managing the interdependencies of power, performance, thermal, and cost in advanced packaging. Core Functionality & Key Features: 1. System-Level Planning & Architecture Exploration This module enables early-stage decision-making, which is crucial for cost and performance. Chiplet Partitioning & Stacking Exploration: Allows architects to evaluate different die partitioning schemes, 2.5D/3D stacking options, and interposer configurations to optimize for performance, power, and manufacturability. System Performance &...